January 20, 2026 by Polytechnic University of Milan

Collected at: https://techxplore.com/news/2026-01-smart-chip-consumption-advancing-high.html

A new chip aims to dramatically reduce energy consumption while accelerating the processing of large amounts of data.

A paper on this work appears in the journal Nature Electronics.

The chip was developed by a group of researchers from the Department of Electronics, Information and Bioengineering–DEIB at the Politecnico di Milano, led by Professor Daniele Ielmini, with researcher Piergiulio Mannocci as the first author.

The work originated as part of the ANIMATE (ANalog In-Memory computing with Advanced device TEchnology) project, which drew on Daniele Ielmini’s preliminary research into CL-IMC (Closed-Loop In-Memory Computing) and the opportunities it could offer, i.e., faster solving of calculations and use of up to 5,000 times less energy than digital computers. The goal of the ANIMATE project was to develop the technology for the device, the circuits and system architectures, and the set of applications to validate the CL-IMC.

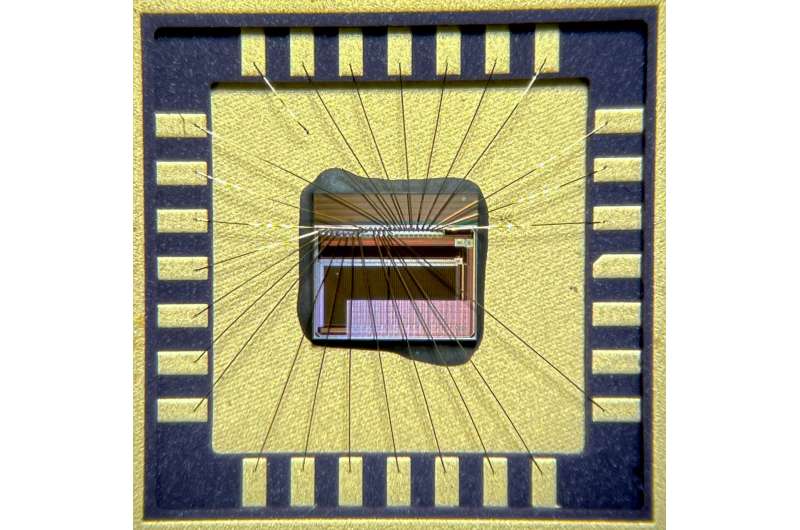

The integrated experimental chip, connected to the carrier chip via wire bonding, for the testing and characterization phases. Credit: Politecnico di Milano

How the chip’s architecture works

The resulting chip makes use of in-memory computing, which aims to overcome a limitation of computers: the need to continuously move data between the memory and the processor. After eliminating this internal traffic, the systems become faster and more energy efficient.

In the recently published study, the DEIB team has presented a fully integrated analog accelerator for solving linear and non-linear systems of equations designed with CMOS (complementary metal-oxide-semiconductor) technology, implemented as standard for the production of silicon integrated circuits.

The device uses two 64×64 arrays of programmable resistive memory. An array is a kind of ordered grid made up of identical parts arranged in rows and columns, similar to graph paper, where each intersection between a row and a column represents a memory cell. The cells are based on SRAM (static random-access memory) technology, a type of fast and stable memory that in this case is combined with integrated resistors for programming different levels of resistance.

The architecture is complemented by an innovative model of analog processing that utilizes components integrated in the chip, such as operational amplifiers and analog-to-digital converters.

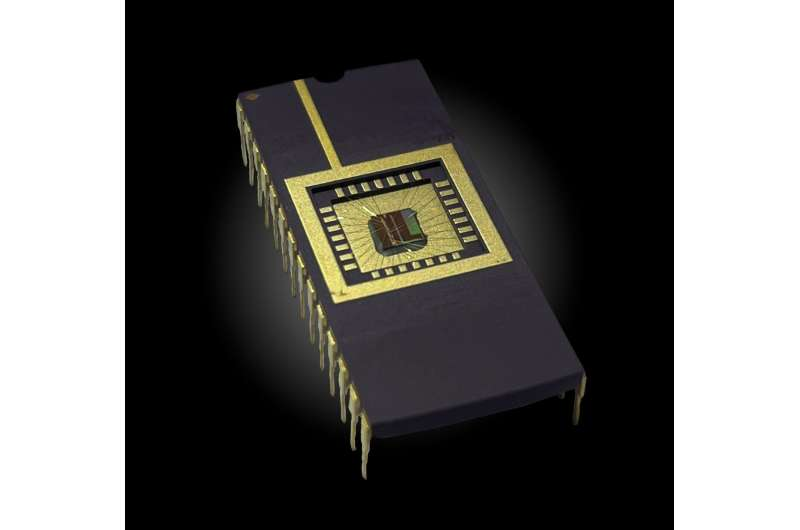

The chip mounted on the characterization board used for the experimental measurements and demonstrations presented in the study. Credit: Politecnico di Milano

Performance, potential and future applications

The set allows the system to handle complex calculations directly in the structure of the memory, avoiding the need to move data to an external processor, thereby reducing calculation times to a significant extent. In tests, the chip achieved similar accuracy to conventional digital systems, but with lower power consumption, less computing latency and a smaller footprint on the silicon.

Ielmini, a member of DEIB and head of the research group, explained, “The integrated chip demonstrates the feasibility on an industrial scale of a revolutionary concept such as analog computation in memory. We are already working on putting this innovation into use in real-world applications to reduce the energy costs of computation, especially in the field of artificial intelligence.”

Mannocci, a researcher for DEIB, commented, “This work is the result of an international collaboration between academia and industry that has also involved Peking University, a diverse team involving professors, researchers, Ph.D. candidates and students, and demonstrates the potential of analog in-memory computation for high-performance, energy-efficient applications.”

The study represents an important step towards more compact, faster and sustainable devices, opening up new perspectives for research and industry. In-memory computing is an ideal solution.

In fact, in contexts requiring high performance and high energy efficiency, such as artificial intelligence, the processing of large volumes of data, and next-generation wireless communication systems. Applications range from robotics to data centers and from navigation systems to advanced telecommunications networks, such as 5G and the 6G technologies of the future.

More information: Piergiulio Mannocci et al, A fully integrated analogue closed-loop in-memory computing accelerator based on static random-access memory, Nature Electronics (2026). DOI: 10.1038/s41928-025-01549-1

Journal information: Nature Electronics

Leave a Reply