December 8, 2025 by Yale University

Collected at: https://techxplore.com/news/2025-12-team-chips-brains-scalable.html

Developing chips that simulate how the brain works has great promise for AI, robotics, and other fields. But making them so that they’re scalable while providing repeatable results has proven tricky. Now, a Yale-led team of researchers has put forth a solution. The results are published in Nature Communications.

Neuromorphic chips—custom integrated circuits that mimic how the brain works—are used to study brain computation and develop neuroscience-inspired artificial neural networks. While not exactly replicas of the human brain, multiple chips can be interconnected to create large-scale systems with more than a billion artificial neurons. Each of these neurons processes information by “spiking” individually. In doing so, neuromorphic systems use up much less energy due to sparse, event-driven operation and can outperform conventional computing systems on specific types of tasks, such as distributed computing workloads.

A significant problem with these chips, though, is that they typically rely on global synchronization protocols for repeatability—that is, a mechanism known as a global barrier synchronizes all the chips’ artificial neurons and synapses. This limits the chips’ scalability, partly because having a single synchronization mechanism ensures that the chip can be only as fast as its slowest component. Also, the additional overhead of global synchronization must propagate across the entire system.

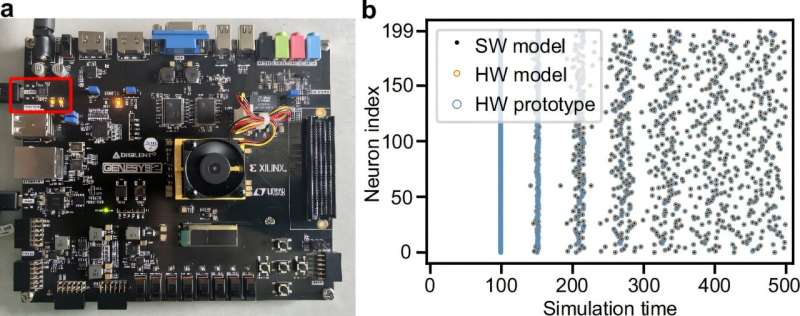

To solve this, a team of Yale researchers led by Prof. Rajit Manohar developed their own system, called NeuroScale. Rather than relying on a global barrier to synchronize all components, NeuroScale synchronizes individual clusters of neurons and synapses that are directly connected to each other.

“Our NeuroScale uses a local, distributed mechanism to synchronize cores,” said Congyang Li, a Ph.D. candidate and lead author of the paper.

The researchers say the main benefit of this innovation is scalability. “Our approach is only limited by the same scaling laws that would apply to the biological network being modeled,” the researchers report.

Going forward, Li said they plan to fabricate the NeuroScale chip, moving from simulation and prototype to silicon implementation. They’re also developing a hybrid approach that combines the synchronization mechanisms of NeuroScale with those of conventional neuromorphic chips.

More information: Congyang Li et al, A deterministic neuromorphic architecture with scalable time synchronization, Nature Communications (2025). DOI: 10.1038/s41467-025-65268-z

Journal information: Nature Communications

Leave a Reply